文章来源:学习那些事

原文作者:小陈婆婆

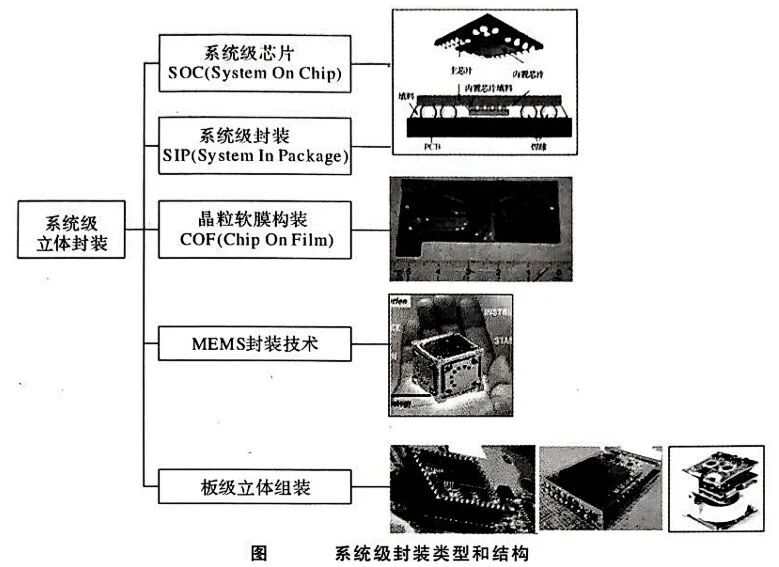

本文介绍了系统级立体封装技术的技术发展与应用。

系统级立体封装技术作为后摩尔时代集成电路产业的核心突破方向,正以三维集成理念重构电子系统的构建逻辑。

该技术通过垂直堆叠与异构集成,在有限物理空间内实现多芯片、无源器件及MEMS/光电器件的高度协同,突破传统单片集成制程瓶颈。

本文分述如下:

系统级封装进展简述

系统级芯片SOC

系统级封装SiP

晶粒软膜构装COF

MEMS封装

板级立体组装

系统级封装进展简述

2025年数据显示,中国先进封装市场规模已突破1100亿元,占全球比例超25%,其中系统级封装(SiP)与2.5D/3D封装增速分别达23%与20.9%,成为驱动增长的双引擎。

技术演进呈现三大特征:空间维度上,3D TSV技术实现芯片间微米级垂直互连,如华为海思通过多层堆叠使芯片体积缩小40%而性能提升30%;效率维度上,倒装芯片与混合键合技术将信号传输延迟降低60%,能效比提升35%;系统维度上,Chiplet标准化推动异构集成成本下降30%,长电科技XDFOI平台实现20μm间距微缩,通富微电VISionS技术攻克2.5D中介层量产难题。

产业生态呈现“设计-制造-封装”三角重构特征,台积电CoWoS平台占据AI芯片封装超60%市场份额,而中国产业链通过“长三角200公里封装产业带”形成材料-设备-制造的完整配套,封装基板国产化率突破40%,关键材料如ABF载板本地供应比例达55%。

未来趋势聚焦三大方向:智能封装通过集成传感器与自适应算法实现实时热管理与性能调节,如英特尔Foveros Direct技术实现10μm凸点间距;标准化进程加速,UCIe规范推动Chiplet全球互连,长电科技XDFOI方案已支持国产CPU芯粒集成;环保维度则聚焦玻璃基板替代,其10层RDL布线与80%热膨胀系数匹配度提升,为3D封装提供可持续解决方案。

此等技术革新不仅重塑半导体产业格局,更在6G通信、工业互联网、可植入医疗设备等新兴领域开辟万亿级市场空间,成为数字经济时代硬件创新的基石。

系统级芯片SOC

系统级芯片(SOC)作为集成电路领域的技术巅峰,正以“单芯多能”的特性重塑电子系统架构。其核心价值在于将中央处理器(CPU)、数字信号处理器(DSP)、图形处理器(GPU)、存储控制器、高速接口及专用逻辑单元等核心功能模块集成于单一硅片,通过片上系统(On-Chip)互连实现高带宽、低延迟的协同运算,满足网络服务器千兆级数据处理、电信基站多模态信号转换、5G/6G基站毫米波通信及高性能计算(HPC)的严苛需求。

技术实现层面,先进制程节点(如5nm及以下)与三维堆叠技术的融合,使SoC在10mm×10mm级晶圆上集成超200亿晶体管,配合倒装芯片(Flip Chip)BGA封装及700+焊球阵列,实现信号传输密度提升40%而功耗降低30%。然而,工艺兼容性瓶颈仍存——SiGe、GaAs与CMOS工艺的互斥性,限制了异构射频前端与数字基带的单片集成,促使业界探索硅基异构集成方案。

未来趋势聚焦三大方向:一是工艺协同创新,如三星2nm GAA工艺与背面供电(BSPD)技术结合,提升SOC能效比;二是标准化推进,UCIe 2.0规范支持Chiplet级SoC互连,实现跨工艺、跨节点的模块化设计;三是可持续封装,玻璃基板替代有机基板,其100μm级通孔与低热膨胀系数(CTE)匹配,为高密度SoC提供更优散热与可靠性保障。此等技术演进不仅推动半导体产业向“更小、更快、更智能”方向发展,更在边缘计算、工业物联网、可穿戴医疗设备等新兴领域催生万亿级市场机遇,成为数字经济时代硬件创新的战略支点。

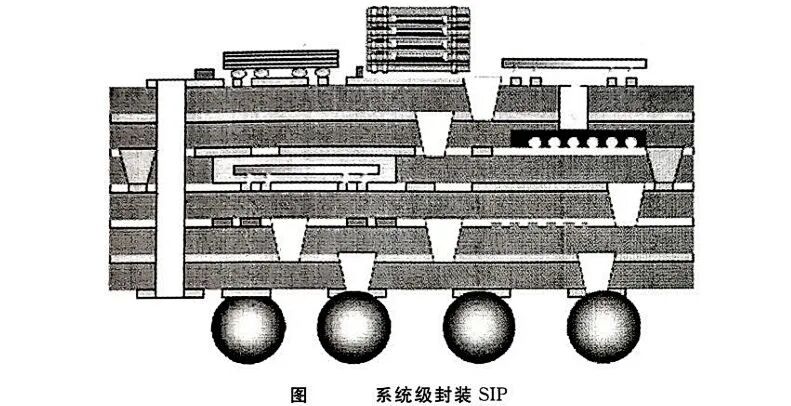

系统级封装SiP

系统级封装(SiP)作为三维集成技术的核心载体,正以“异构协同”理念重构电子系统的构建范式,在无线通信、消费电子及新兴智能终端领域展现出不可替代的战略价值。其本质是通过晶圆级堆叠、基板嵌入式集成及混合互连技术,将CPU、DSP、存储器、射频前端、MEMS传感器及无源器件等模块整合于单一封装体内,突破单片集成工艺壁垒,实现高频高速、低功耗与高密度的系统级功能集成。

技术实现层面,SiP的灵活性体现在多维异构集成能力——通过晶片堆叠(如TSV垂直互连)可实现10μm级芯片间距,配合倒装芯片(Flip Chip)与引线键合(Wire Bonding)的混合互连,既满足GHz级高频RF模块(如GaAs功率放大器与CMOS基带芯片的集成)的信号完整性要求,又适配低频数字模块的成本敏感需求;基板选择则涵盖高性能ABF载板(支持20μm线宽/间距)与常规CSP基片,前者在AI计算模块中实现HBM内存与GPU的2.5D互连,后者则在消费级TWS耳机中完成蓝牙SoC与电源管理芯片的紧凑集成。

在5G通信领域,村田制作所采用嵌入式基板技术的SiP模组,将PA、LNA、滤波器及双工器集成于3.5mm×3.5mm封装内,满足Sub-6GHz频段毫米波前端的小型化需求;在AIoT边缘端,联发科Filogic系列SiP通过异构集成CPU、NPU、Wi-Fi 6/6E基带及电源管理单元,实现单芯片支持智能家居网关的复杂计算任务;医疗可穿戴设备中,美敦力采用生物兼容封装与低功耗设计的SiP传感器,集成ECG、PPG及温度监测功能,体积缩减至传统方案60%而续航提升40%。

未来趋势聚焦三大创新方向:一是工艺标准化,UCIe 2.0规范推动Chiplet级SiP互连,实现跨工艺、跨节点的模块化设计;二是材料革新,玻璃基板替代有机基板,其100μm级通孔与低热膨胀系数(CTE)匹配,为高密度SiP提供更优散热与可靠性保障;三是智能封装,集成温度传感器与自适应算法,实现实时热管理与性能调节,如英特尔Foveros Direct技术在SiP中嵌入热敏电阻,动态调整工作频率以优化能效比。此等技术演进不仅推动半导体产业向“更小、更快、更智能”方向发展,更在6G原型验证、工业物联网节点及植入式医疗设备等前沿领域开辟万亿级市场空间,成为数字经济时代硬件创新的战略支点。

晶粒软膜构装COF

晶粒软膜构装(COF)作为柔性电子封装的标杆技术,正以“刚柔并济”的集成理念重塑显示与智能终端的物理边界。该技术通过将芯片直接贴装于柔性聚酰亚胺(PI)基材,实现高密度互连与三维立体布线,突破传统玻璃基板(CoG)在面板边缘走线密度与分辨率的限制——相同尺寸面板下,COF方案可扩展超30%的像素密度,支撑4K/8K超高清显示及窄边框设计,成为LED/OLED显示模组、可折叠手机及车载HUD的核心封装方案。

技术演进呈现三大创新维度:材料层面,新型低温固化胶粘剂与高延伸率PI薄膜的应用,使COF在-40℃至125℃宽温域下保持99.9%的连接可靠性,满足汽车级AEC-Q100认证;工艺层面,激光微孔成型与电镀铜柱技术实现15μm级线宽/间距,配合倒装芯片(Flip Chip)键合,使单颗芯片引脚密度提升40%而厚度缩减至0.3mm以下;系统集成层面,COF与嵌入式无源器件(如薄膜电容、电阻)的一体化封装,在TWS耳机、智能手表等紧凑空间内实现电源管理、触控传感及射频前端的协同集成,如苹果AirPods Pro 2即采用COF-SIP混合封装,体积缩减20%而功能密度提升35%。

在显示领域,京东方8.5代COF生产线支持Mini LED背光模组量产,实现2000分区局部调光;在车载电子中,天马微电子采用COF封装的曲面屏HUD,在150℃高温环境下保持85%透光率与170°广视角;医疗可穿戴方面,华米科技基于COF的ECG贴片,集成生物电极与信号处理芯片,实现心电信号采集精度达医疗级ECG-12标准。

未来趋势聚焦三大方向:一是超薄化,通过玻璃基转印技术与纳米压印工艺,实现50μm级超薄COF制造;二是智能化,集成温度/压力传感器与自适应算法,动态调整封装应力与信号传输;三是可持续化,采用可回收PI基材与无铅焊料,满足欧盟RoHS 3.0及REACH法规要求。此等技术革新不仅推动显示产业向“更薄、更柔、更智能”演进,更在元宇宙终端、柔性机器人皮肤及生物医疗植入等前沿领域开辟增量市场,成为柔性电子时代硬件创新的基石。

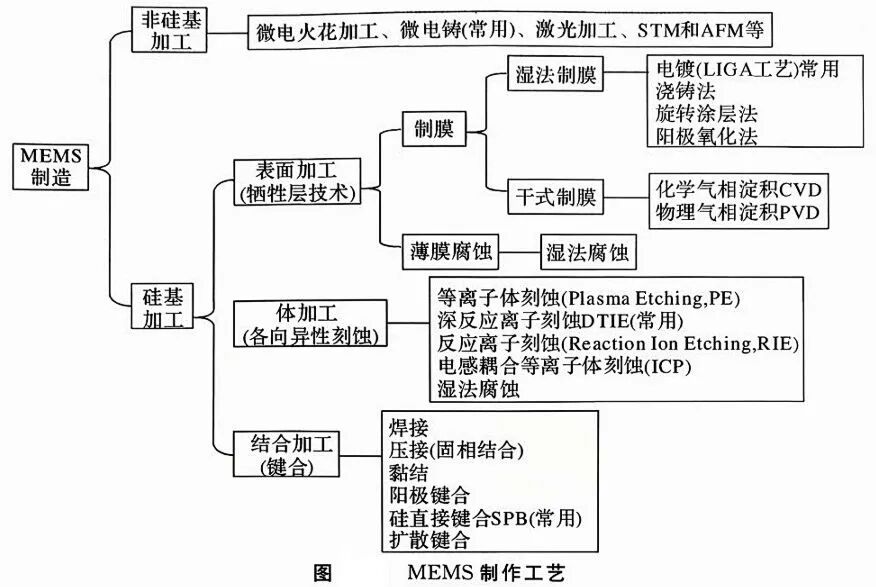

MEMS封装

微机电系统(MEMS)封装技术作为连接微纳器件与系统应用的桥梁,正以“高精度、高可靠、高集成”为核心演进方向,在医疗、汽车、工业等领域的精密感知需求驱动下实现多维突破。

技术革新层面,三维集成与材料创新成为双引擎。多光子光刻技术实现纳米级分辨率三维微结构直写,如压阻式加速度计通过飞秒激光三维直写完成从设计到制造的2.5小时全流程,性能媲美传统数月迭代方案;晶圆级真空键合技术通过低温阳极键合(350℃/600V)与钛吸气剂活性保持,实现硅-玻璃键合腔体压力稳定在5mTorr以下,配合梯度退火工艺通过3000次,-40℃~125℃热循环测试,解决传统环氧树脂封装的气密性瓶颈。键合工艺方面,Au-Sn共晶键合通过瞬态液相扩散技术填补0.5μm级表面粗糙度,键合强度达50MPa以上,配合0.8mm键合环宽度实现10⁻⁸atm·cc/s级漏率标准,适配陀螺仪、压力传感器等对真空环境的严苛需求;而引线键合通过反向拱丝工艺压缩线弧高度至50μm,结合动态压力反馈系统将键合定位误差控制在±1μm,良率提升至99.2%,满足5G通信器件0.5mm超薄封装要求。

产业生态呈现“设计-制造-封装”垂直整合趋势。中国长三角地区形成完整产业链集群,封装基板国产化率突破40%,关键材料如ABF载板本地供应比例达55%;行业联盟推动MIPI传感器接口规范统一,UCIe 2.0标准支持Chiplet级MEMS互连,实现跨工艺、跨节点模块化设计;智能化封装方面,集成温度/压力传感器与自适应算法,动态调节封装应力与信号传输,如英特尔Foveros Direct技术实现10μm凸点间距,配合嵌入式无源器件实现电源管理、触控传感一体化集成。未来,随着玻璃基板替代有机基材(100μm级通孔与低热膨胀系数匹配)、纳米银焊膏低温键合(150℃以下避免生物蛋白损伤)等技术的突破,MEMS封装将从“保护性封装”向“功能增强型封装”跃迁,在元宇宙光波导扫描、人形机器人柔性感知、绿色能源微流控等新兴领域开辟万亿级增量市场,成为数字经济时代精密感知的核心基础设施。

板级立体组装

板级立体组装作为三维电子系统构建的关键技术路径,正以“空间重构”理念突破传统二维PCB布线局限,在高铁控制模块、5G基站阵列、数据中心冷板系统等高密度、高性能场景中展现核心价值。其本质是通过垂直互连、凸点连接及侧向键合技术,实现多块PCB模块在三维空间中的精准堆叠与电气-机械协同,在有限物理空间内实现信号传输密度提升30%—50%,同时降低系统热阻与信号延迟。

技术演进呈现三大创新维度:材料层面,纳米银浆低温烧结技术实现150℃以下互连,避免传统焊料导致的热应力损伤,配合石墨烯散热涂层使模块热阻降低40%,适配高铁IGBT模块的高温运行需求;工艺层面,3D打印PCB技术通过光固化成型实现50μm级线宽/间距,配合激光微孔成型与电镀铜柱技术,实现垂直互连层间通孔的100%良率,如中兴通讯5G基站模块通过该技术实现6层PCB堆叠,信号传输延迟降低至2ps/cm;系统集成层面,嵌入式无源器件(如薄膜电容、电阻)与有源芯片的一体化封装,在单模块内集成电源管理、射频前端及数字处理功能,如华为数据中心硅光引擎通过板级立体组装实现光模块与CPU的垂直互连,带宽密度提升50%而功耗降低30%。

未来趋势聚焦三大方向:一是智能化制造,通过数字孪生技术实现板级立体组装的虚拟仿真与实时优化,如西门子NX软件支持3D PCB布线与热管理协同设计;二是标准化推进,IPC-4101规范推动板级立体组装材料与工艺的统一,UCIe 3.0标准支持跨模块、跨节点的互连设计;三是可持续化,采用可回收PCB基材与无铅焊料,满足欧盟RoHS 3.0及REACH法规要求。此等技术革新不仅推动电子制造产业向“更密、更快、更绿”方向发展,更在6G原型验证、工业物联网节点及绿色能源微电网等前沿领域开辟万亿级增量市场,成为数字经济时代硬件创新的战略支点。