在高速、高密度的PCB设计项目中,工程师的设计早已迈入了另外一个台阶——从“连通即可”的基础要求,跃迁至以规则驱动、以仿真验证、以工艺为导向的精密设计时代。

本文基于 Allegro X Designer 的核心功能,从规则管理、布线效率、叠层设计这三个方面入手,剖析贯穿整个设计流程的专业设计体系。

本文要点

key point

一文看懂 Allegro XDesigner系统级电路设计解法

约束管理器:实现设计的规则定义与管理,让你的规则设计从手动检查升级为驱动整个设计的自动化管理引擎

智能交互式布线:拥有智能感知、自动优化能力,实现布线约束的高效落地。

层叠编辑器:提供叠层设计、阻抗计算与材料管理,解决信号设计中的信号完整性、电源完整性等问题。

问题点1:线宽、间距的定义凭经验感觉至上,遵循“差不多”原则

在高速数字电路设计中,工程师常凭经验设置线宽、间距,但当信号速率攀升至GHz级别、叠层结构复杂时,"差不多"的规则往往成为信号完整性失效的导火索。更棘手的是,不同网络(如DDR数据组、时钟、差分对)对规则要求差异极大,手动维护极易出错;板子的布线常常占据整个项目周期的50%,手动推挤调整已有布线、调整过孔繁琐且易出错;叠层设计仅凭工程师的经验估算可能会导致加工后的板子的阻抗与设计预期偏差较大,导致整块板子成为废板。

时钟线长度超限:PCB走线的时候因板子空间有限常常布线超过一定的长度,未考虑终端匹配以及缓冲问题,导致信号传播延迟过大,引起反射和过冲,损坏驱动端或接收端的IO电路。

信号线走线之间的线宽过窄:在一定的阻抗下,线距过窄会导致信号反射和功率损耗,长期工作会有PCB板过热烧毁的风险。

过孔使用不当:高速信号布线时使用了常规的通孔,存在一部分的过孔残桩导致阻抗不连续,从而引起信号反射和插入损耗。

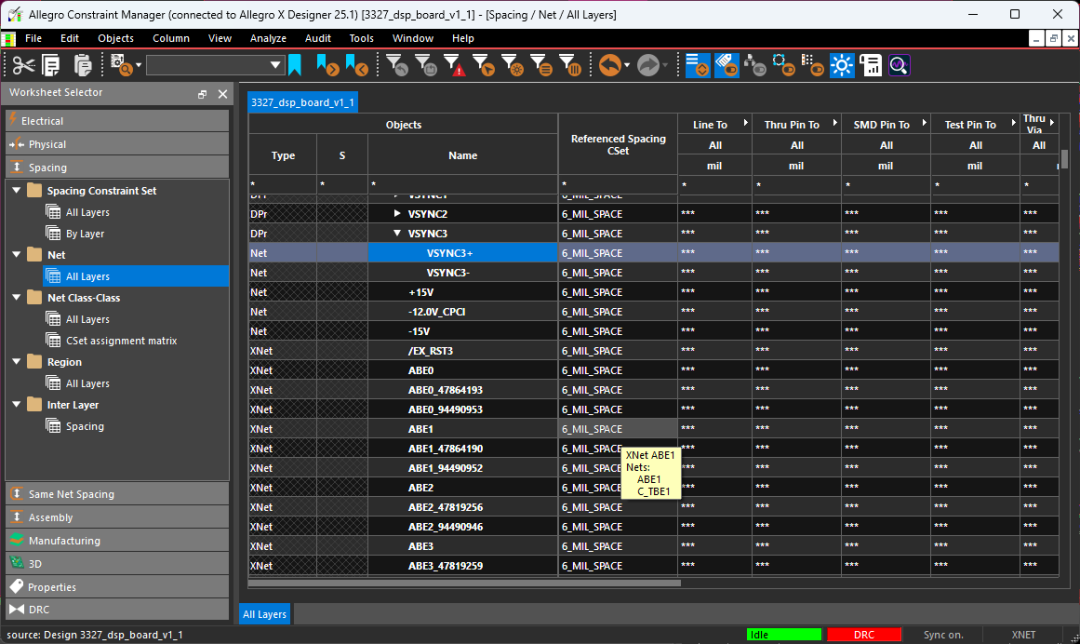

针对电气、物理、间距这三类约束相关的问题,Allegro X Designer提供了系统级的预防手段——Constraint Manager(约束管理器)。

通过这一集中化的规则定义中枢,工程师可将信号完整性、制造工艺、安全规范等多维度要求转化为层级化的规则体系,涵盖电气约束(线长、等长、延迟)、物理约束(线宽、间距、过孔类型)以及间距约束(不同网络类之间的安全距离)。

同时,约束管理器与 Sigrity 信号完整性仿真引擎、PCB 制造工艺数据库无缝对接,可自动调用基于真实板材参数和叠层结构的阻抗计算模型,并结合板厂实际工艺能力进行规则校验,从而在设计阶段就将经验规则固化为可执行、可复用的设计标准,彻底告别“凭感觉、差不多设规则”的被动局面。

问题点2:新增、调整布线太过随意,布线调整效率低

传统“先布后调”方式:布线时未启用自动推挤功能,新增走线与相邻走线之间的距离小于设计规则要求,形成串扰以及短路风险。

线间间距不均与等长失控:数据线之间的线距不均导致部分区域的串扰,差分信号未使用等长布线导致后期后期等长差异过大导致信号衰减严重等。

针对提高布线效率、进行间距优化等问题,Allegro X Designer 内置一套完整的交互式布线引擎和约束驱动设计环境。半自动等长绕线功能支持多种绕线模式(波浪形、锯齿形、阶梯形),在布线过程中实时显示剩余长度,并可一键生成符合公差的绕线方案;动态推挤布线(Push&Shove)则让新增走线时自动调整周边线段,始终保持线宽、间距与设计规则一致,彻底告别“先布后调"带来的反复修线。自动修线优化工具(Auto Gloss)可在布线完成后一键消除锐角、直角等不良拐角,并将走线圆滑处理,从而将工程师从“手工推线、目测等长、反复返工”的重复劳动中解放出来,使布线效率提升50%以上,同时确保信号完整性与设计规范的高度一致性。

问题点3:依靠经验或简单工具估算层叠参数,引发信号反射、串扰

层叠不对称导致PCB板翘曲:在设计多层板的时候,顶层和底层的铜厚分布不均会导致 PCB 在回流焊过程中受热时,上下表面膨胀系数不一致而造成生成出来的 PCB 板子不符合国际标准。

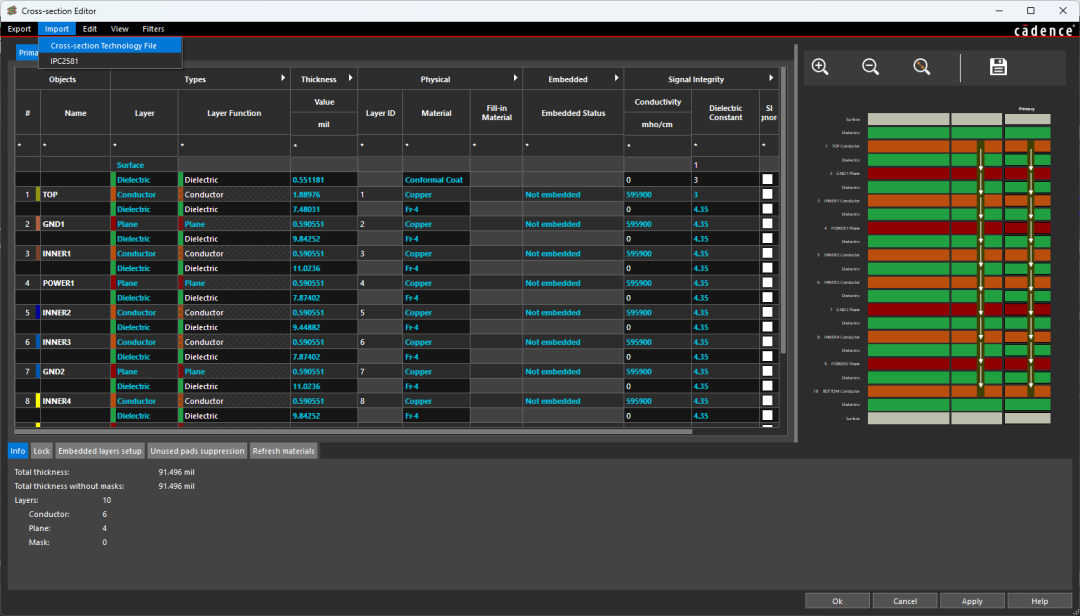

在叠层编辑界面,工程师可直接设定每层的介质厚度、铜厚、介电常数等参数,系统实时计算微带线、带状线等常见结构的特征阻抗值,并自动关联到约束管理器的阻抗规则中;同时允许工程师预设生产厂家的加工工艺参数(如蚀刻补偿、压合厚度、铜箔粗糙度等),使阻抗计算与叠层设计更贴近实际制造能力,从源头减少“设计-制造”偏差。此外,叠层对称性与平衡性检查功能可自动检测叠层结构是否存在翘曲风险,实时提供优化建议,确保板厂加工良率。

针对复杂的PCB设计流程,需要严格把控每个关键环节,构建系统化的体系。Allegro X Designer 提供了一套深度融合的解决方案,助力工程师在设计源头筑牢防线:通过Constraint Manager约束管理器建立层级化的电气、物理、间距规则体系,将设计意图转化为可执行的自动化管控;借助智能布线引擎与半自动等长绕线系统,将推挤避让、多线并行、等长匹配等复杂操作融入交互式布线环境,彻底告别“先布后调、手工修线”的低效模式;利用叠层编辑器(Cross Section) 内置的材料库、工艺参数预设及对称性检查功能,使叠层设计与阻抗计算精准对齐制造能力,从物理基础上保障信号完整性与可制造性。帮助每一位深耕技术领域的专家在下一次设计中更加出彩。